MSc thesis project proposal

Towards brain-inspired AI hardware

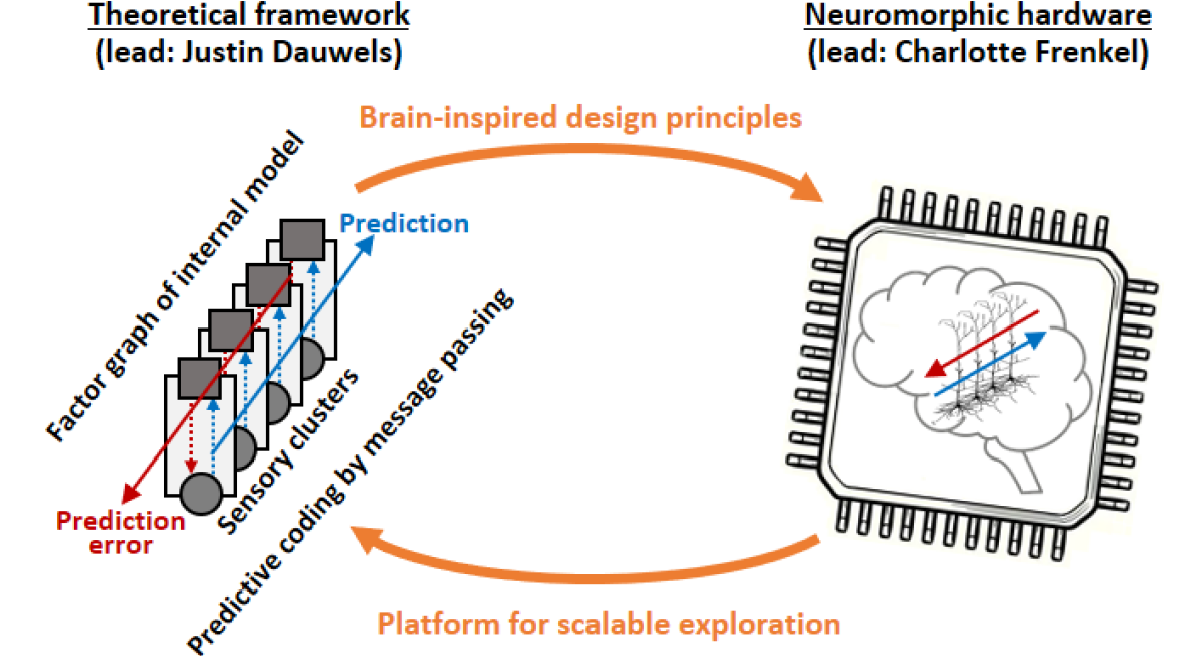

Building autonomous agents that can reliably compute and take decisions in noisy and uncontrolled environments is among the top research areas in today's artificial intelligence (AI). To do so, an online and real-time form of adaptation is needed. There are currently two major algorithmic approaches to implement learning and plasticity:

- the error backpropagation algorithm, the workhorse of modern deep learning, offers top performance but typically requires high-performance GPUs,

- local brain-inspired learning rules can run on low-cost custom neuromorphic hardware [1], but scaling them to real-world tasks is difficult.

In this MSc project, we will investigate graphical models, which are the state-of-the-art approach to Bayesian inference and have recently led to efficient model-based signal processing and machine learning algorithms [2]. In particular, factor graphs are graphical models that visualize the factorization of the system model and allow for a divide-and-conquer approach to learn complex models from data. Many state-of-the-art algorithms in signal processing and machine learning can be viewed as the computation of messages on factor graphs of the system at hand [2,3]. Crucially, the resulting message-passing algorithms only involve local computations, thereby offering the missing bridge between the two major algorithmic approaches outlined above.

Based on the resulting local rules, a hardware-algorithm co-design approach will be pursued [4], with the objective to design a digital proof-of-concept hardware that demonstrates scalable local learning rules toward low-cost autonomous AI hardware that can adapt to uncontrolled environments.

[1] C. Frenkel et al., "A 0.086-mm² 12.7-pJ/SOP 64k-synapse 256-neuron online-learning digital spiking neuromorphic processor in 28-nm CMOS," IEEE Transactions on Biomedical Circuits and Systems, vol. 13, no. 1, pp. 145-158, 2019.

[2] H.-A. Loeliger, J. Dauwels, J. Hu, S. Korl, L. Ping and F. R. Kschischang, "The Factor Graph Approach to Model-Based Signal Processing," Proceedings of the IEEE, vol. 95, no. 6, pp. 1295-1322, 2007.

[3] J. Dauwels, "On Variational Message Passing on Factor Graphs," IEEE International Symposium on Information Theory, pp. 2546-2550, 2007.

[4] C. Frenkel, Charlotte and G. Indiveri, "ReckOn: A 28nm Sub-mm² Task-Agnostic Spiking Recurrent Neural Network Processor Enabling On-Chip Learning over Second-Long Timescales," IEEE International Solid-State Circuits Conference (ISSCC), 2022.

Requirements

For this multi-disciplinary project, background in machine learning and digital design is required. It is strongly advised to follow the following courses:

- EE4685: Machine learning, a Bayesian perspective (given in Q3),

- ET4351: Digital VLSI systems on chip (given in Q4).

This project will be supervised by Dr. Charlotte Frenkel (EI section) and Dr. Justin Dauwels (SPS section).

Interested students should send a motivation letter together with their CV (incl. course transcripts and grades) at c.frenkel@tudelft.nl and j.h.g.dauwels@tudelft.nl.

Contact

dr.ir. Justin Dauwels

Signal Processing Systems Group

Department of Microelectronics

Last modified: 2024-02-27